Mohammadsadegh Sadri

PhD, University of Bologna, Italy

Post Doctoral Researcher, TU Kaiserslautern, Germany

March – 20 - 2014

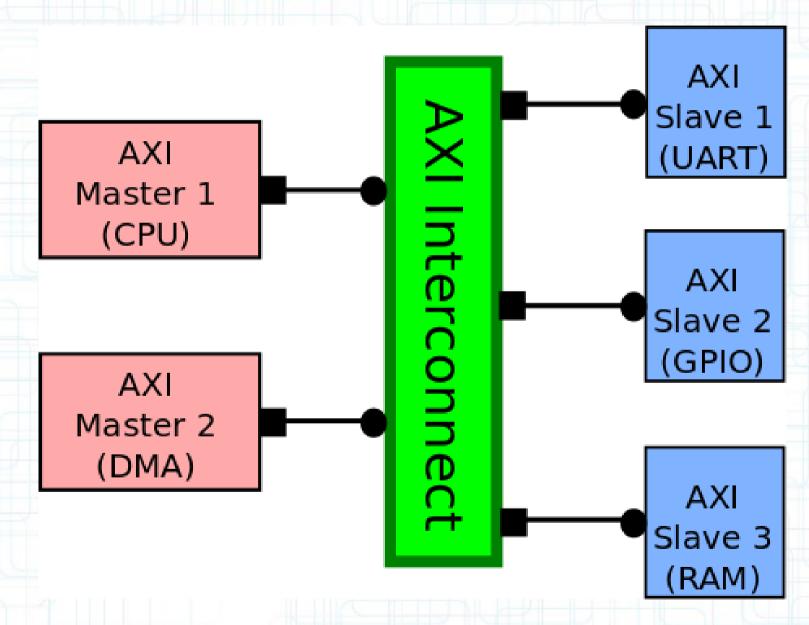

# **Connecting Masters & Slaves**

AXI Master 1 (CPU)

AXI Master 2 (DMA) AXI Slave 1 (UART)

AXI Slave 2 (GPIO)

AXI Slave 3 (RAM)

#### **AXI Interconnect**

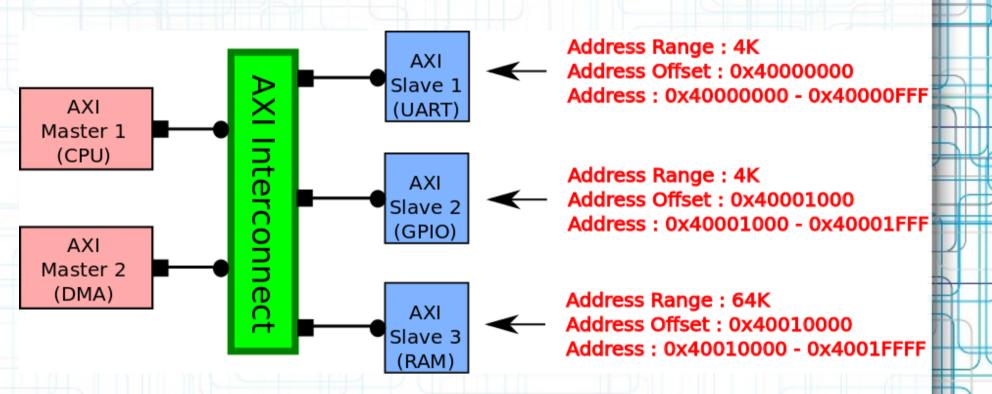

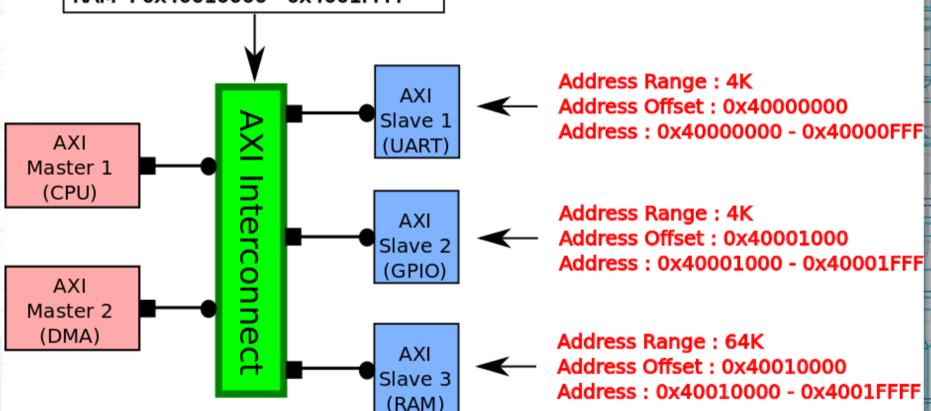

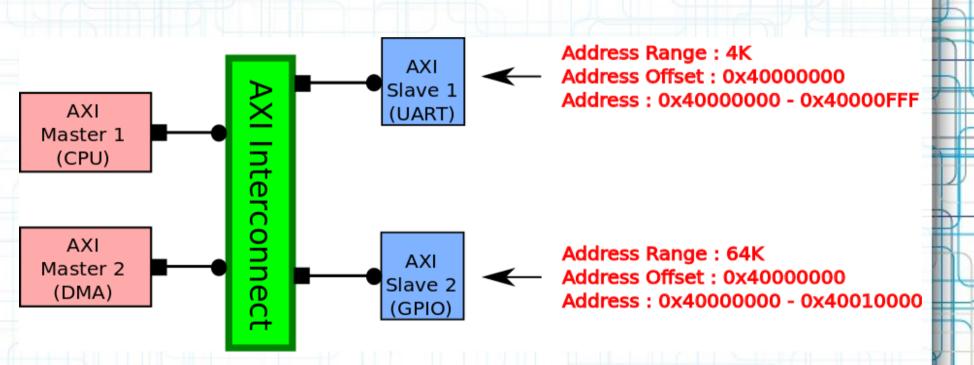

# Addressing...

# AXI Interconnect Address Decoding

#### Address Decoding Table

UART: 0x40000000 - 0x40000FFF

GPIO: 0x40001000 - 0x40001FFF

RAM: 0x40010000 - 0x4001FFFF

Mohammad S. Sadri – What is an AXI Interconnect?

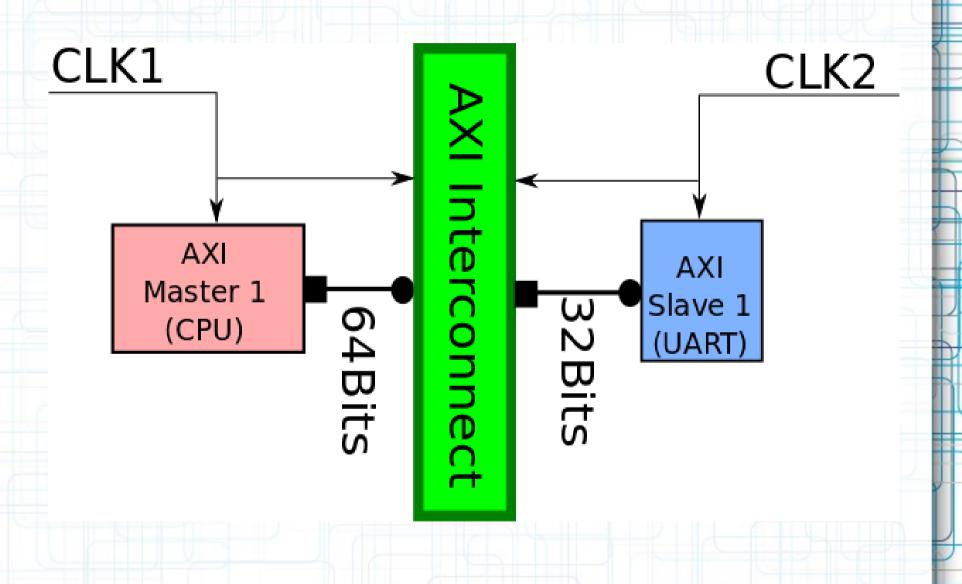

## **AXI Interconnect**

- Different number of

- Slave and Master Ports

- Width Conversion

- AXI3 to AXI4

- Register slices, Input/output FIFOs

- Clock Domain Transformation

#### **AXI Interconnect**

Mohammad S. Sadri – What is an AXI Interconnect?

#### **Hierarchical AXI Interconnects AXI** Slave 1 **AXI Interconnect** AXI (UART) Master 0 (CPU2) **AXI** Slave 2 (ETH) AXI AXI Interconnect Slave 3 AXI (USB) Master 1 (CPU) AXI Slave 4 (GPIO) AXI Master 2 (DMA) **AXI** Slave 5 (RAM) Mohammad S. Sadri – What is an AXI March - 20th - 2014 Interconnect?

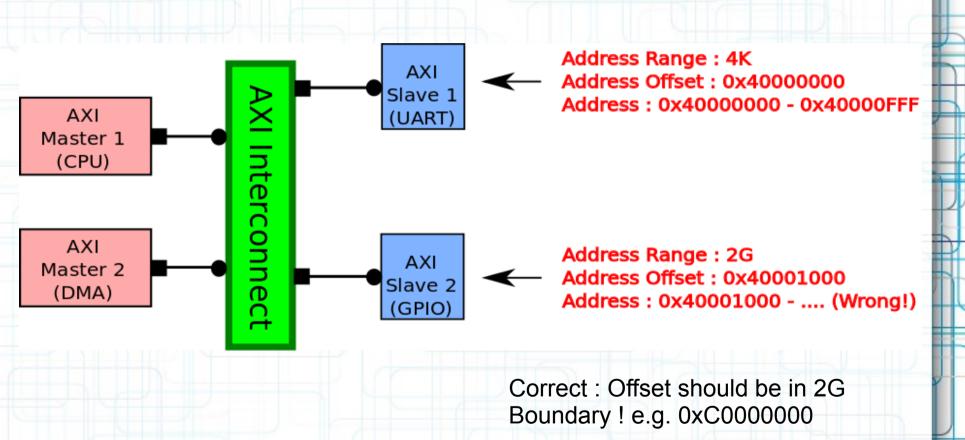

# Simple Address Definition Rules

No overlaps

# Simple Address Definition Rules

Meet required alignment in Address

#### Thanks ...

This is a personal hobby! But I would like to thank

- Prof. Luca Benini, of University of Bologna & ETHZ

- Prof. Norbert Wehn of TU Kaiserslautern

### **Latest Material** ...

My personal web sites:

www.green-electrons.com

www.googoolia.com